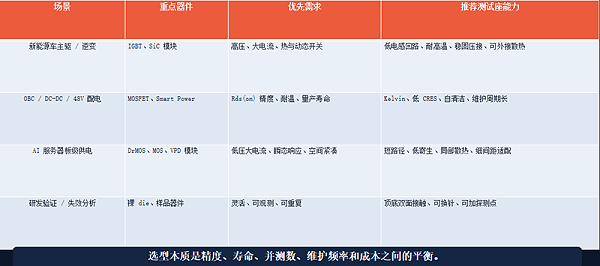

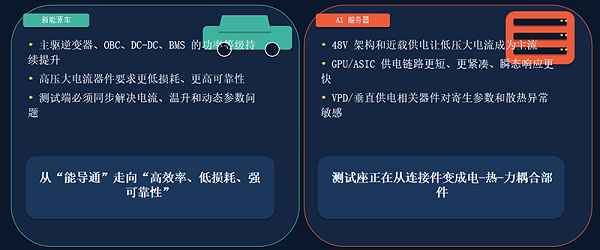

功率芯片的测试可靠性,直接决定芯片研发验证的准确性与量产交付的合格率,而芯片测试座作为连接芯片与测试系统的核心接口,其性能稳定性更是关键支撑。当前,新能源车、AI服务器等场景对功率芯片的高效率、低损耗、强可靠性要求持续提升,测试座的失效的不仅会导致测试数据失真、误判,更可能延误研发周期、增加量产成本。

需特别强调的是,功率芯片测试座的验证绝非“首件导通即合格”,必须同时覆盖电性能、热稳定性、机械结构三个维度——电性能保障测试精度,热稳定性适配芯片高功耗场景,机械结构确保长期接触可靠,三者缺一不可。鸿怡电子凭借多物理场耦合设计优势,将测试座的技术特性与三维验证深度融合,从源头规避失效风险,提升测试全流程稳定性。

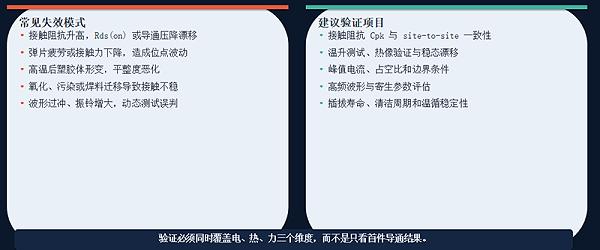

一、功率芯片测试座常见失效模式及核心诱因

功率芯片测试过程中,测试座的失效多源于电、热、力三维性能的失衡,结合新能源车高压大电流、AI服务器低压高频的应用场景,以下5类失效模式最为典型,且易被“首件导通”的表面结果误导。

(一)接触阻抗升高,Rds(on)或导通压降漂移

这是最常见的电性能失效,核心诱因包括探针接触不良、引脚氧化、接触表面污染等。在高压大电流测试场景中,接触阻抗升高会导致导通损耗增加,进而引发Rds(on)(导通电阻)或导通压降异常漂移,使得芯片效率评估失真——看似导通合格的芯片,实际应用中可能因损耗超标导致发热严重、寿命缩短。例如新能源车SiC芯片测试中,接触阻抗仅升高5mΩ,就可能导致导通压降漂移超过10%,直接影响测试数据的有效性。

(二)弹片疲劳或接触力下降,造成位点波动

属于机械结构失效,主要源于测试座弹片的材料疲劳、插拔次数过多或设计不合理。弹片作为接触的核心部件,其接触力直接决定接触稳定性,当弹片疲劳、接触力下降时,会导致芯片引脚与探针的接触点位不稳定,出现测试数据波动(如同一芯片多次测试的参数偏差超过5%),尤其在高频动态测试中,位点波动会直接导致开关参数误判,影响芯片驱动电路的优化设计。

(三)高温后塑胶体形变,平整度恶化

属于热-力耦合失效,适配功率芯片高功耗、宽温域测试场景(如新能源车-40℃~150℃温循测试、AI服务器芯片长期高温运行测试)。测试座塑胶体若材料耐热性不足、热膨胀系数(CTE)不匹配,在高温环境下会发生不可逆形变,导致座体平整度恶化,进而引发探针与芯片引脚对位偏差、接触压力不均,最终出现接触不良、参数漂移等连锁失效。

(四)氧化、污染或焊料迁移导致接触不稳

属于电-化学失效,多发生在长期量产测试或恶劣测试环境中。测试座接触表面若未做特殊防护,易被空气中的水汽、灰尘污染,或出现引脚氧化、焊料迁移现象,导致接触电阻不稳定、间歇性导通,甚至出现“测试合格、实际应用失效”的隐患——例如AI服务器低压大电流测试中,焊料迁移会导致局部接触电阻突变,引发电源模块开关振荡。

(五)波形过冲、振铃增大,动态测试误判

属于电-力耦合失效,核心诱因是测试座寄生电感、寄生电容过高,或阻抗匹配不合理。在高频动态测试(如SiC芯片开关参数测试、AI服务器高频信号交互测试)中,过高的寄生参数会导致测试波形出现过冲、振铃,使得di/dt、dv/dt等关键动态参数测量失真,进而误判芯片性能,导致不合格芯片流入市场,或优质芯片被误判为不合格。

二、电-热-力三维验证项目(鸿怡电子功率芯片测试座协同应用)

针对上述失效模式,验证项目必须突破“只看导通”的局限,从电性能、热稳定性、机械结构三个维度全面覆盖,结合鸿怡电子功率芯片测试座的技术设计,实现“失效可预防、性能可验证、数据可追溯”,以下6大核心验证项目可精准规避各类失效风险。

(一)接触阻抗Cpk与site-to-site一致性验证(电维度核心)

该项目核心验证测试座接触的稳定性与一致性,直接针对“接触阻抗升高、参数漂移”失效模式。传统测试仅测量单点接触阻抗,易遗漏接触不良隐患,而鸿怡电子功率芯片测试座通过专属设计,与验证流程深度协同,实现全面验证。

协同应用亮点:鸿怡测试座采用镀金铍铜/钨铜合金探针,接触阻抗稳定控制在5mΩ以下,搭配碳纤维-殷钢基板的精准定位设计,可确保多测试位点(site)的接触阻抗一致性。验证过程中,借助鸿怡测试座的多通道测试功能,可同步检测所有位点的接触阻抗,计算Cpk值(过程能力指数),确保Cpk≥1.33,site-to-site之间的阻抗偏差≤3%,从源头规避接触阻抗升高导致的Rds(on)、导通压降漂移问题。同时,测试座探针表面的防氧化涂层设计,可有效减少氧化、污染带来的接触不稳,延长验证周期。

(二)温升测试、热像验证与稳态漂移验证(热-电耦合核心)

该项目针对“高温塑胶体形变、导通损耗发热”失效模式,同时验证热稳定性与电性能稳态性,是电-热维度的关键验证环节。功率芯片测试中,测试座的散热能力与热稳定性,直接影响芯片结温与测试参数的稳定性。

协同应用亮点:鸿怡电子针对高功耗场景设计的散热型测试座,预留液冷/风冷安装窗口,搭配阳极氧化铝合金外壳(兼具散热与绝缘功能),可快速导出芯片测试过程中产生的热量。验证时,通过热像仪实时监测测试座座体、探针及芯片表面的温升情况,确保稳态测试时座体温升≤15℃,芯片结温控制在安全阈值内;同时,结合鸿怡测试座的宽温适配能力(-55℃~175℃),完成温循测试后的稳态参数漂移验证,确保漂移量≤2%,避免高温形变、温升过高导致的接触不良与参数失真。

(三)峰值电流、占空比和边界条件验证(电-力耦合核心)

该项目针对“大电流下接触失效、参数漂移”失效模式,模拟功率芯片实际应用中的极端工况,验证测试座的大电流承载能力与边界条件适应性,覆盖电性能与机械结构的双重验证。

协同应用亮点:鸿怡功率芯片测试座单pin过流能力可达10A@800V(新能源车场景)、1000A连续大电流(AI服务器场景),探针的弹性结构设计可承受大电流下的接触应力。验证过程中,结合鸿怡测试座的大电流适配能力,模拟芯片实际工作中的峰值电流、最大占空比,以及高低温、高压等边界条件,测试接触阻抗的稳定性、参数漂移情况,确保测试座在极端工况下仍能保持可靠接触,避免大电流导致的弹片变形、接触力下降。

(四)高频波形与寄生参数评估(电-力耦合核心)

该项目针对“波形过冲、振铃增大”失效模式,核心验证测试座的寄生参数控制能力与阻抗匹配精度,是高频动态测试的关键验证环节,直接影响动态参数测量的准确性。

协同应用亮点:鸿怡电子针对高频场景推出的低寄生测试座,采用同轴探针结构,寄生电感控制在0.1nH以下,特性阻抗精准匹配50Ω,可有效抑制高频信号的反射与串扰。验证时,借助鸿怡测试座的高频适配能力,测试高频波形的过冲幅度、振铃次数,评估寄生电感、寄生电容对动态参数的影响,确保过冲幅度≤5%,振铃次数≤2次,避免动态测试误判,为芯片高频性能优化提供精准数据支撑。

(五)插拔寿命、清洁周期和温循稳定性验证(力-热耦合核心)

该项目针对“弹片疲劳、高温形变、接触不稳”失效模式,验证测试座的机械耐久性与环境适应性,覆盖机械结构与热稳定性的双重要求,直接关系到量产测试的效率与成本。

协同应用亮点:鸿怡功率芯片测试座的弹片采用高强度铍铜合金,经过疲劳强化处理,插拔寿命可达50万次以上,远超行业常规标准(30万次);座体采用耐高温、低CTE材料,可有效避免高温形变。验证过程中,通过模拟量产测试中的插拔频率,确定测试座的清洁周期(鸿怡测试座可实现1万次插拔无明显污染,清洁周期延长50%);同时,完成-55℃~175℃的温循测试(≥1000次),验证座体平整度、弹片接触力的稳定性,确保温循后接触力下降≤10%,平整度偏差≤5μm,避免弹片疲劳、高温形变导致的位点波动与接触不良。

(六)三维协同验证闭环(电-热-力整合)

上述5项验证项目并非孤立存在,需通过三维协同验证形成闭环——例如,在大电流峰值测试中,同步监测接触阻抗(电)、座体温升(热)、弹片接触力(力);在温循测试后,同步验证接触一致性(电)、平整度(力)、稳态参数漂移(电-热)。鸿怡电子功率芯片测试座可与各类测试设备无缝对接,支持多参数同步采集,实现电-热-力三维数据的联动分析,精准定位潜在失效隐患,确保测试座的综合性能满足功率芯片的测试需求。

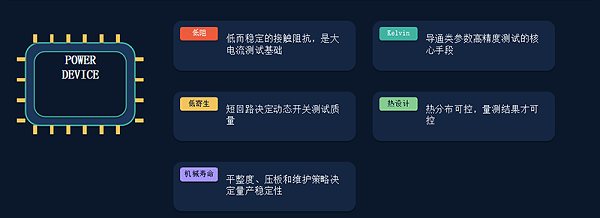

三、鸿怡电子测试座的失效预防优势与应用价值

鸿怡电子功率芯片测试座的核心价值,在于将“失效预防”融入产品设计,与三维验证项目深度协同,从源头降低失效概率,同时提升验证效率、降低验证成本。

从失效预防来看,鸿怡测试座通过材料创新(耐高温、低CTE基板、高强度探针)、结构优化(低寄生同轴设计、双散热路径)、表面防护(防氧化、防污染涂层),针对性规避了接触阻抗升高、弹片疲劳、高温形变等5类常见失效;从验证协同来看,测试座的技术参数与验证项目精准匹配,可直接适配各类验证场景,无需额外适配调试,将验证周期缩短30%以上,同时确保验证数据的准确性与可靠性。

在实际应用中,某新能源车SiC芯片量产测试项目中,借助鸿怡测试座的三维验证协同能力,将接触不良导致的测试误判率降至0.01%以下;某AI服务器电源芯片研发项目中,通过鸿怡测试座的寄生参数评估的高频波形验证,成功规避了波形振铃导致的动态参数误判,研发周期缩短25%。

功率芯片测试座的失效,本质是电、热、力三维性能失衡的结果,而“只看首件导通”的片面验证,只会埋下测试失真、应用失效的隐患。唯有建立电-热-力三维验证体系,针对性覆盖接触阻抗、温升、寄生参数、机械耐久性等核心项目,才能从根本上规避失效风险。

鸿怡电子功率芯片测试座以多物理场耦合设计为核心,与三维验证项目深度协同,既解决了传统测试座的常见失效痛点,又通过技术创新提升了验证效率与可靠性,为功率芯片研发验证与量产测试提供了稳定、精准的接口支撑。未来,随着功率芯片向更高功率、更高频率、更宽温域发展,鸿怡电子将持续优化测试座的设计与验证方案,进一步强化电-热-力三维协同能力,助力功率芯片实现高效率、低损耗、强可靠性的核心目标。